# Lecture Notes in Computer Science 2210 Edited by G. Goos, J. Hartmanis, and J. van Leeuwen

# Springer Berlin

Berlin Heidelberg New York Barcelona Hong Kong London Milan Paris Tokyo Yong Liu Kiyoshi Tanaka Masaya Iwata Tetsuya Higuchi Moritoshi Yasunaga (Eds.)

# Evolvable Systems: From Biology to Hardware

4th International Conference, ICES 2001 Tokyo, Japan, October 3-5, 2001 Proceedings

#### Volume Editors

Yong Liu

University of Aizu

Tsuruga, Ikki-machi, Aizu-Wakamatsu City, Fukushima 965-8580, Japan

E-mail: yliu@u-aizu.ac.jp

Kiyoshi Tanaka

Shinshu University, Faculty of Engineering 4-17-1 Wakasato, Nagano 380-8553, Japan E-mail: ktanaka@gipwc.shinshu-u.ac.jp

Masaya Iwata, Tetsuya Higuchi

Nat. Inst. of Adv. Ind. Science and Technology, Adv. Semiconductor Research Center

AIST Tsukuba Central 2, 1-1-1 Umezono, Tsukuba, Ibaraki 305-8568, Japan

E-mail: {m.iwata/t-higuchi}@aist.go.jp

Moritoshi Yasunaga

University of Tsukuba, Institute of Information Sciences and Electronics

Tsukuba, Ibaraki 305-8573, Japan E-mail: yasunaga@is.tsukuba.ac.jp

#### Cataloging-in-Publication Data applied for

Die Deutsche Bibliothek - CIP-Einheitsaufnahme

Evolvable systems : from biology to hardware ; 4th international conference ; proceedings / ICES 2001, Tokyo, Japan, October 3 - 5, 2001. Yong Liu ... (ed.). - Berlin ; Heidelberg ; New York ; Barcelona ; Hong Kong ; London ;

Milan; Paris; Tokyo: Springer, 2001

(Lecture notes in computer science; Vol. 2210)

ISBN 3-540-42671-X

CR Subject Classification (1998): B.6, B.7, F.1, I.6, I.2, J.2, J.3

ISSN 0302-9743

ISBN 3-540-42671-X Springer-Verlag Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable for prosecution under the German Copyright Law.

Springer-Verlag Berlin Heidelberg New York a member of BertelsmannSpringer Science+Business Media GmbH

http://www.springer.de

© Springer-Verlag Berlin Heidelberg 2001 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Steingräber Satztechnik GmbH, Heidelberg Printed on acid-free paper SPIN: 10840795 06/3142 5 4 3 2 1 0

#### **Preface**

On behalf of the ICES 2001 Conference Committee, it is our pleasure to present to you the proceedings of the fourth International Conference on Evolvable Systems: From Biology to Hardware, ICES 2001, held in Tokyo, Japan, on 3-5 October 2001, addressing the latest developments and discussing challenges facing the field of evolvable systems.

The idea of evolving machines, whose origins can be traced back to the cybernetics movement of the 1940s and the 1950s, has recently re-emerged in the form of the nascent field of bio-inspired systems and evolvable hardware. Following the workshop, Towards Evolvable Hardware, which took place in Lausanne, Switzerland, in October 1995, the First International Conference on Evolvable Systems: From Biology to Hardware (ICES96), was held at the Electrotechnical Laboratory (MITI), Tsukuba, Japan, in October 1996. The second and the third International Conferences on Evolvable Systems: From Biology to Hardware (ICES98 and ICES 2000) were respectively held in Lausanne in September 1998, and in Edinburgh in April 2000.

Following the success of these past events, ICES 2001 was dedicated to the promotion and advancement of all aspects of evolvable systems, including hardware, software, algorithms, and applications. By bringing together researchers who use biologically inspired concepts to implement real systems in artificial intelligence, artificial life, robotics, VLSI design, and related domains, ICES 2001 reunited this burgeoning community.

High quality papers were selected and presented at the conference. These contributions cover a wide variety of aspects pertaining to evolvable systems and applications: evolutionary design of electronic circuits, embryonic electronics, biological-based systems, evolutionary robotics, evolutionary optimization, evolutionary learning, and the various applications of evolvable hardware.

We wish to thank all the authors for submitting their work, as well as the Program Committee members and reviewers for their enthusiasm, time, and expertise. Finally, we would like to thank the sponsors, who helped in one way or another to achieve our goals for the conference. These sponsors are Real World Computing Partnership, the Japanese Society for Artificial Intelligence, SIG on AI Challenges, Logic Systems Laboratory (EPFL), and the National Institute of Advanced Industrial Science and Technology (AIST).

August 2001

Yong Liu Kiyoshi Tanaka Masaya Iwata Tetsuya Higuchi Moritoshi Yasunaga

## Organization

#### ICES 2001 Conference Committee

General chair: Tetsuya Higuchi, National Institute of Advanced Industrial Science and Technology (AIST), Japan

Program co-chair: Daniel Mange, Swiss Federal Institute of Technology, Switzerland

Program co-chair: Moritoshi Yasunaga, University of Tsukuba, Japan

Program co-chair: Yong Liu, University of Aizu, Japan Publicity chair: Kiyoshi Tanaka, Shinshu University, Japan Finance chair: Hiroshi Okuno, Kyoto University, Japan

Local chair: Masaya Iwata, National Institute of Advanced Industrial Science

and Technology (AIST), Japan

Conference secretary: Ayako Suzuki, National Institute of Advanced Industrial Science and Technology (AIST), Japan

#### ICES 2001 Program Committee

Peter Dittrich, University of Dortmund, Germany

Rolf Drechsler, Albert-Ludwigs-University, Germany

Tim Goredon, University College London, U.K.

Pauline Haddow, Norwegian University of Science and Technology (NTNU), Norway

Alister Hamilton, Edinburgh University, U.K.

Masaya Iwata, National Institute of Advanced Industrial Science and Technology (AIST), Japan

Isamu Kajitani, National Institute of Advanced Industrial Science and Technology (AIST), Japan

Tatiana Kalganova, Brunel University, U.K.

Lishan Kang, Wuhan University, P. R. China

Michael Korkin, Genobyte, Inc., U.S.A.

Pierre Marchal, Centre Suisse d'Electronique et de Microtechnique, Switzerland Karlheinz Meier, University of Heidelberg, Germany

David Montana, BBN Technologies Robert Popp, U.S.A.

Masahiro Murakawa, National Institute of Advanced Industrial Science and Technology (AIST), Japan

Andres Perez-Uribe, University of Fribourg, Switzerland

Hidenori Sakanashi, National Institute of Advanced Industrial Science and Technology (AIST), Japan

Eduardo Sanchez, Swiss Federal Institute of Technology, Switzerland

Moshe Sipper, Swiss Federal Institute of Technology, Switzerland

Kiyoshi Tanaka, Shinshu University, Japan

Gianluca Tempesti, Swiss Federal Institute of Technology, Switzerland

#### VIII Organization

Adrian Thompson, University of Sussex, U.K. Jim Torresen, University of Oslo, Norway Andy Tyrrell, University of York, U.K. Milan Vasilko, Bournemouth University, U.K. Xin Yao, University of Birmingham, U.K.

# Table of Contents

| Evolutionary Design of Electronic Circuits                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------|

| Two-Step Incremental Evolution of a Prosthetic Hand Controller Based on Digital Logic Gates                                           |

| Untidy Evolution: Evolving Messy Gates for Fault Tolerance                                                                            |

| Evolutionary Design Calibration                                                                                                       |

| Implementation of a Gate-Level Evolvable Hardware Chip                                                                                |

| A VLSI Implementation of an Analog Neural Network Suited for Genetic Algorithms                                                       |

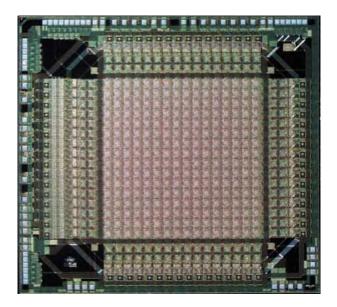

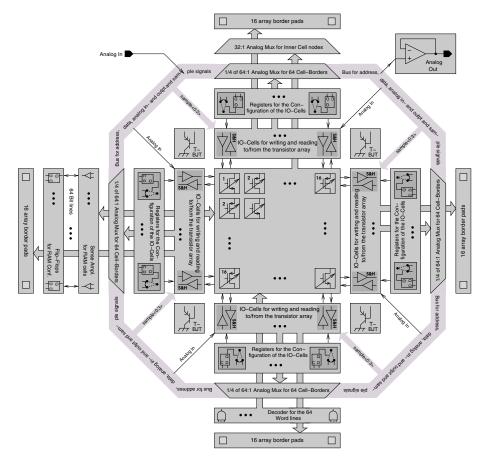

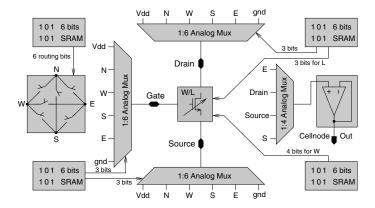

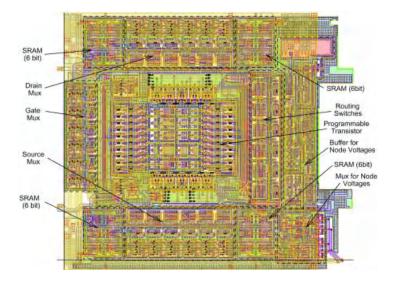

| Initial Studies of a New VLSI Field Programmable Transistor Array 62  J. Langeheine, J. Becker, S. Fölling, K. Meier, and J. Schemmel |

| Embryonic Electronics                                                                                                                 |

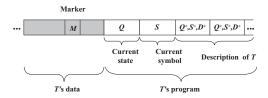

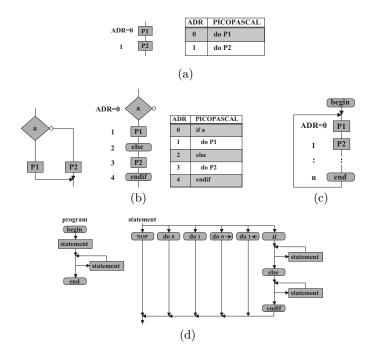

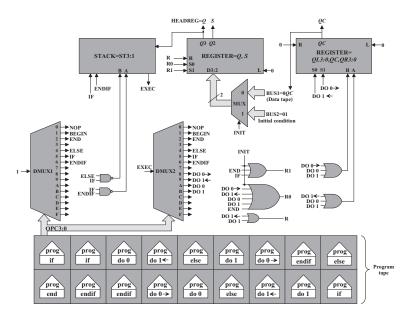

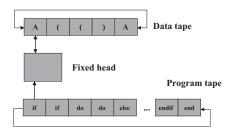

| An Embryonics Implementation of a Self-Replicating Universal Turing Machine                                                           |

| Asynchronous Embryonics with Reconfiguration                                                                                          |

| Embryonics: Artificial Cells Driven by Artificial DNA                                                                                 |

| Biological-Based Systems                                                                                                              |

| A Self-Repairing and Self-Healing Electronic Watch: The BioWatch 112 A. Stauffer, D. Mange, G. Tempesti, and C. Teuscher              |

| Shrinking the Genotype: L-systems for EHW?                                                                                            |

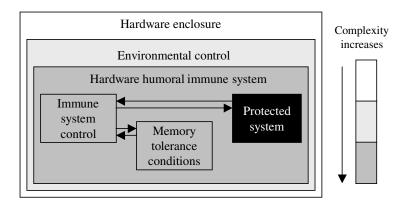

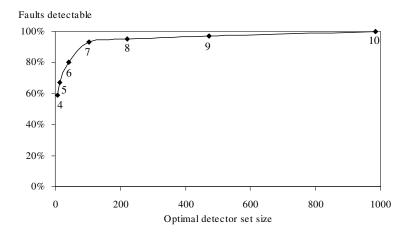

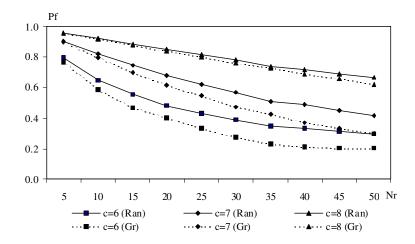

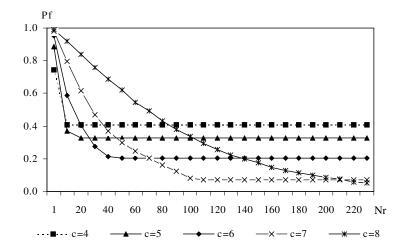

| Multi-layered Defence Mechanisms: Architecture, Implementation and Demonstration of a Hardware Immune System                          |

| Ant Circuit World: An Ant Algorithm MATLAB <sup>TM</sup> Toolbox for the Design, Visualisation and Analysis of Analogue Circuits  |

|-----------------------------------------------------------------------------------------------------------------------------------|

| Evolutionary Robotics                                                                                                             |

| Human-Like Dynamic Walking for a Biped Robot Using Genetic Algorithm                                                              |

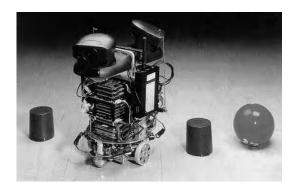

| Effect of Fitness for the Evolution of Autonomous Robots in an Open-Environment                                                   |

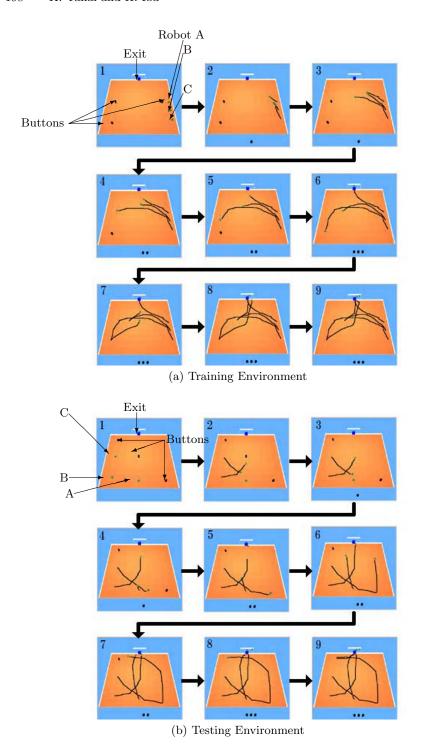

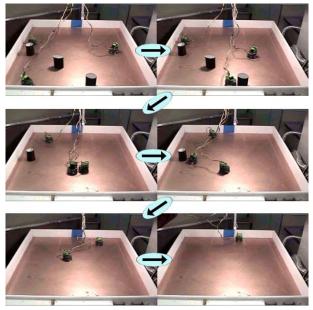

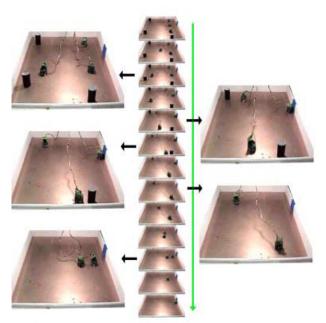

| Incremental Evolution of Autonomous Robots for a Complex Task 182 Md.M. Islam, S. Terao, and K. Murase                            |

| Multi-agent Robot Learning by Means of Genetic Programming:  Solving an Escape Problem                                            |

| Evolutionary Optimization                                                                                                         |

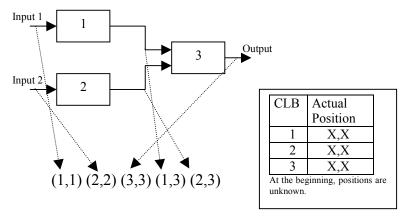

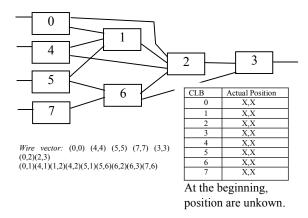

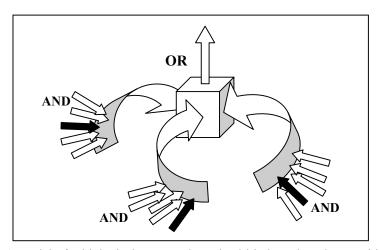

| Placing and Routing Circuits on FPGAs<br>by Means of Parallel and Distributed Genetic Programming                                 |

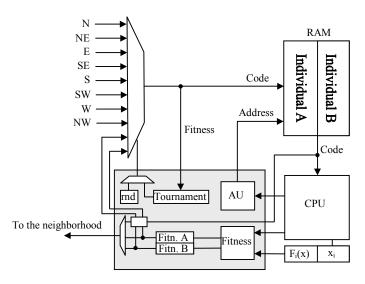

| A Massively Parallel Architecture for Linear Machine Code Genetic Programming                                                     |

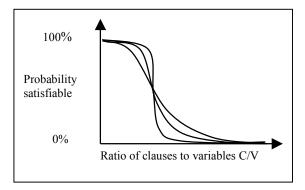

| Self-Organized Evolutionary Process in Sets of Interdependent Variables near the Midpoint of Phase Transition in K-Satisfiability |

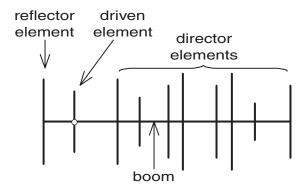

| Evolutionary Optimization of Yagi-Uda Antennas                                                                                    |

| Evolutionary Learning                                                                                                             |

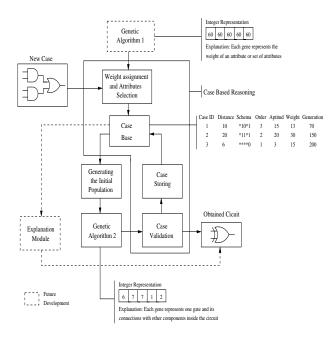

| Extraction of Design Patterns from Evolutionary Algorithms Using Case-Based Reasoning                                             |

| Balancing Samples' Contributions on GA Learning                                                                                   |

| Solving Partially Observable Problems by Evolution and Learning of Finite State Machines                                          |

| GA-Based Learning of $kDNF_n^s$ Boolean Formulas                                                                      |

|-----------------------------------------------------------------------------------------------------------------------|

| Applications                                                                                                          |

| Polymorphic Electronics                                                                                               |

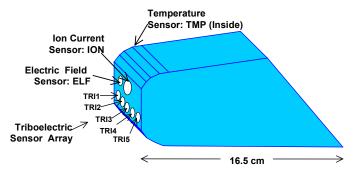

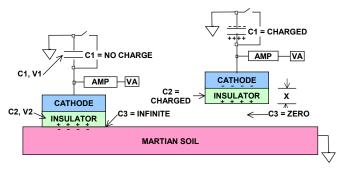

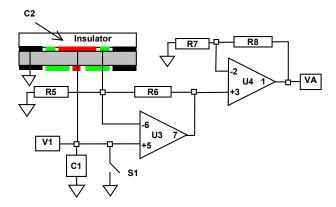

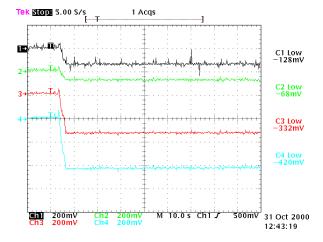

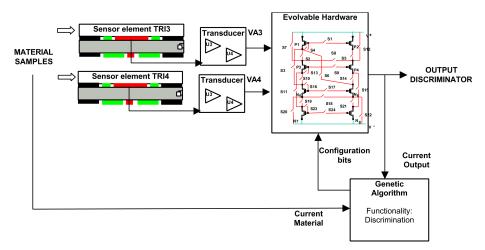

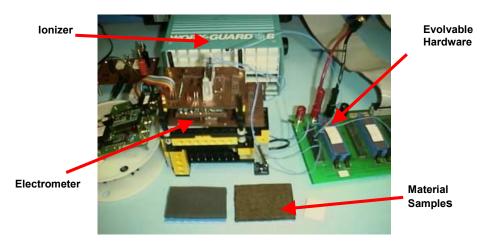

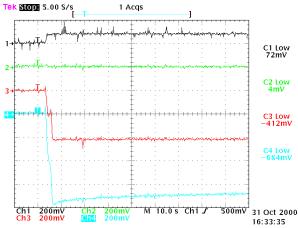

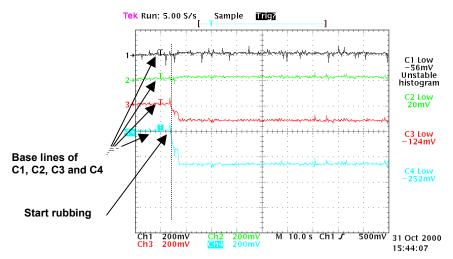

| Initial Experiments of Reconfigurable Sensor Adapted by Evolution 303 D. Keymeulen, R. Zebulum, A. Stoica, M. Buehler |

| A Lossless Compression Method for Halftone Images Using Evolvable Hardware                                            |

| Evolvable Optical Systems and Their Applications                                                                      |

| Author Index 341                                                                                                      |

# Two-Step Incremental Evolution of a Prosthetic Hand Controller Based on Digital Logic Gates

#### Jim Torresen

Department of Informatics, University of Oslo, P.O. Box 1080 Blindern, N-0316 Oslo, Norway, jimtoer@ifi.uio.no, http://www.ifi.uio.no/~jimtoer

**Abstract.** Evolvable Hardware (EHW) has been proposed as a new method for designing systems for real-world applications. In this paper it is applied for evolving a prosthetic hand controller. It is shown that better generalization performance than neural networks can be obtained. The proposed architecture is based on digital logic gates and its configuration is determined by two separate steps of evolution.

#### 1 Introduction

To enhance the lives of people who has lost a hand, prosthetic hands have existed for a long time. These are operated by the signals generated by contracting muscles – named electromyography (EMG) signals, in the remaining part of the arm [1]. Presently available systems normally provide only two motions: Open and close hand grip. The systems are based on the user adapting *himself* to a fixed controller. That is, he must train himself to issue muscular motions trigging the wanted action in the prosthetic hand. Long time is often required for rehabilitation.

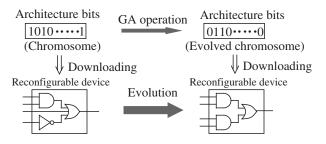

By using Evolvable Hardware (EHW) it is possible to make the *controller* itself adapt to each disabled person. The controller is constructed as a pattern classification hardware which maps input patterns to desired actions of the prosthetic hand. Adaptable controllers have been proposed based on neural networks [2]. These require a floating point CPU or a neural network chip. However, by using gate level EHW, a much more compact implementation can be provided making it more feasible to be installed inside a prosthetic hand.

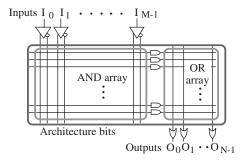

Experiments based the EHW approach have already been undertaken by Kajitani et al [3]. The research on adaptable controllers is based on designing a controller providing six different motions in three different degrees of freedom. Such a complex controller could probably only be designed by adapting the controller to each dedicated user. It consists of AND gates succeeded by OR gates (Programmable Logic Array). The latter gates are the outputs of the controller, and the controller is evolved as one complete circuit. The simulation indicates a similar performance as artificial neural network but since the EHW controller requires a much smaller hardware it is to be preferred.

One of the main problems in evolving hardware systems seems to be the limitation in the chromosome string length [4,5]. A long string is normally required

for representing a complex system. However, a larger number of generations is required by genetic algorithms (GA) as the string increases. This often makes the search space too large. Thus, work has been undertaken to try to diminish this limitation. Various experiments on speeding up the GA computation have been undertaken [6]. The schemes involve fitness computation in parallel or a partitioned population evolved in parallel – by parallel computation. Other approaches to the problem have been by using variable length chromosome [7] and reduced genotype representation [8]. Another option, called function level evolution, is to evolve at a higher level than gate level [9]. Most work is based on fixed functions. However, there has been work in Genetic Programming for evolving the functions [10]. The method is called Automatically Defined Functions (ADF) and is used in software evolution.

Another improvement to artificial evolution – called co-evolution, has been proposed [11]. In co-evolution, a part of the data, which defines the problem, co-evolves simultaneously with a population of individuals solving the problem. This could lead to a solution with a better generalization than a solution evolved based on the initial data. Further overview of related works can be found in [12].

Incremental evolution for EHW was first introduced in [13] for a character recognition system. The approach is a divide-and-conquer on the evolution of the EHW system, and thus, named *increased complexity evolution*. The goal is to develop a scheme that could evolve systems for complex real-world applications. In this paper, it is applied to the application of a prosthetic hand controller circuit. Several improvements in the EHW architecture as well as how incremental evolution is applied are to be introduced. These should improve the generalization performance of gate level EHW and make it a strong alternative to artificial neural networks.

The next two sections introduce the concepts of the evolvable hardware based prosthetic hand controller. Results are given in Section 4 with conclusions in Section 5.

#### 2 Prosthetic Hand Control

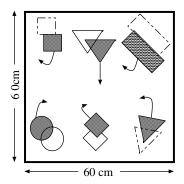

The research on adaptable controllers presented in this paper is based on designing controllers providing six different motions in three different degrees of freedom: Open and Close hand, Extension and Flection of wrist, Pronation and Supination of wrist. The data set consists of the same motions as used in earlier work [3], and it is collected by Dr. Kajitani at Electrotechnical Laboratory in Japan.

The published results on adaptive controllers are usually based on data for non-disabled persons. Since you may observe the hand motions, a good training set can be generated. For the disabled person this is not possible since there is no hand observe. The person would have to by himself distinguish the different motions. Thus, it would be a harder task to get a high performance for such a training set but it will indicate the expected response to be obtainable by the prosthesis user. This kind of training set is applied in this paper. No other

publication is yet available – to make a comparison of the results, where this data set is used.

#### 2.1 Data Set

The absolute value of the EMG signal is integrated for 1 s and the resulting value is coded by *four* bits. To improve the performance of the controller it is beneficial to be using several channels. In these experiments *four* channels were used in total, giving an input vector of  $4 \times 4 = 16$  bits.

The *output* vector consists of one binary output for each hand motion, and therefore, the output vector is coded by six bits. For each vector only *one* bit is "1". Thus, the data set is collected from a disabled person by considering one motion at a time. For each of the six possible motions, a total of 50 data vectors are collected, resulting in a total of:  $6 \times 50 = 300$  vectors. Further, two such sets were made, one to be used for evolution (training) and the others to be used as a separate test set for evaluating the best circuit after evolution is finished.

#### 3 A Gate Architecture for Incremental Evolution

The evolution scheme – introduced as *increased complexity evolution*, has been proposed to overcome the problem of a long chromosome string. The idea is to evolve a system gradually. Evolution is first undertaken individually on a set of basic units. Each of these could contain gates or higher level functions as building blocks. The evolved functions are the basic blocks used in further evolution (or assembly) of a larger and more complex system. This may continue until a final system is at a sufficient level of complexity. In this paper, a novel method applying two separate and succeeding evolution steps are proposed.

#### 3.1 Approaches to Increased Complexity Evolution

The main advantage of the method is that evolution is not performed in one operation on the complete evolvable hardware unit but rather in a bottom-up way. It may be looked at as a division of the *problem* domain. The challenge of the approach would be how to define the fitness functions for the lower level subsystems. Two alternatives seem possible:

- Partitioned training vectors. A first approach to incremental evolution is by partitioning the training vectors. For evolving a truth table - i.e. like those used in digital design, each separate output could be evolved separately. In this method, the fitness function is given explicitly as a subset of the complete fitness function.

- Partitioned training set. A second approach is to divide the training set into several subsets. This corresponds to the way humans learns: Learning to walk and learning to talk are two different learning tasks. The fitness function would have to be designed for each task individually and used together with a global fitness function, when the tasks are to be assembled. This may not be a trivial problem.

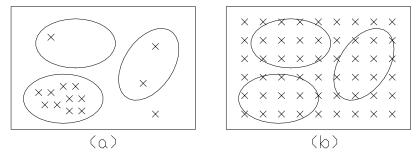

The benefits of applying the *increased complexity evolution* are several:

- Making the search space simpler by having the complexity of the problem to be evolved reduced for each subsystem.

- Making the search space smaller by having a shorter chromosome string.

This is because the circuit is smaller.

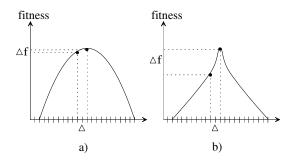

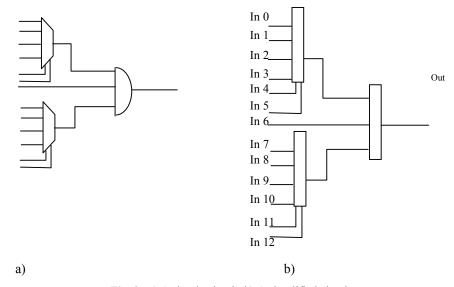

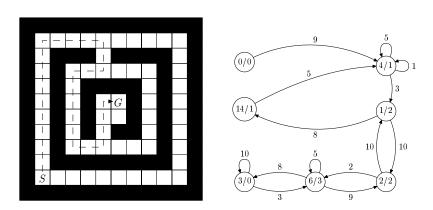

Both of these two items concern the evolutionary search space as illustrated in Fig. 1. A simple search space is shown in Fig. 1a), while a more complex one is given in Fig. 1b). In the former figure, several instances would give a near maximum fitness while it becomes more important hitting the exact maximum in the latter. Thus, when both are having the same deviation  $\triangle$  to reach maximum fitness, there is a large difference in their corresponding fitness deviation  $\triangle$ f. In the proposed method, the complexity of the problem is reduced by reducing the amount of information to be represented in a digital circuit.

The indices along the x-axis indicate the step size in the evolutionary search space. This is given by the chromosome length. A short string would imply a small number of indices compared to a longer string. The former would be more beneficial as this would reduce the search space. Thus, the goal of the *increased complexity evolution* approach is to *both* reduce the number of indices (by having a short chromosome string) as well as making the search space more smooth (by reducing the complexity of the problem to be evolved).

#### 3.2 The Architecture of the Prosthetic Hand Controller

In this section, the proposed architecture for the controller is described. This includes the algorithm for undertaking the incremental evolution.

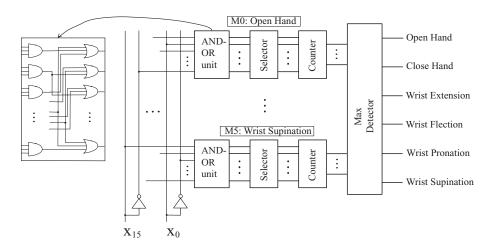

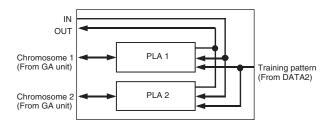

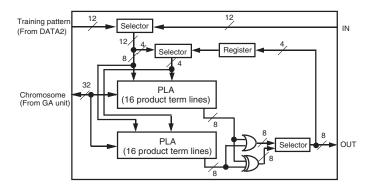

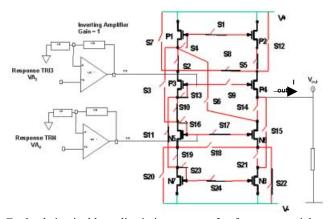

The architecture is illustrated in Fig. 2. It consists of one subsystem for each of the six prosthetic motions. In each subsystem, the binary inputs  $x_0

ldots x_{15}$  are processed by a number of different units, starting by the AND-OR unit. This is a layer of AND gates followed by a layer of OR gates. Each gate has the same number of inputs, and the number can be selected to be two, three or four. The outputs of the OR gates are routed to the Selector. This unit selects which of these outputs that are to be counted by the succeeding counter. That is, for each new input, the Counter is counting the number of selected outputs being

Fig. 1. Illustration of evolutionary search spaces.

Fig. 2. The digital gate based architecture of the prosthetic hand controller.

"1" from the corresponding AND-OR unit. Finally, the Max Detector outputs which counter – corresponding to *one* specific motion, is having the largest value. Each output from the Max Detector is connected to the corresponding motor in the prosthesis. If the Counter having the *largest* value corresponds to the correct hand motion, the input has been correctly classified.

A scheme, based on using multi-input AND gates together with counters, has been proposed earlier [14]. However, the architecture proposed in this paper is distinguished by including OR-gates, together with the selector units involving incremental evolution.

The incremental evolution of this system can be described by the following steps:

- 1. **Step 1 evolution.** Evolve the AND-OR unit for each subsystem *separately* one at a time. Apply *all* vectors in the training set for the evolution of each subsystem. There are no interaction among the subsystems at this step, and the fitness is measured on the output of the AND-OR units. A largest possible number of OR gates should be "1" for the 50 patterns corresponding to the motion the subsystem is set to respond to. For all other patterns, the number of gates outputting "1' should be as small as possible. That is, each subsystem should ideally respond only to the patterns for one specific prosthesis motion.

- 2. **Step 2 evolution.** Assemble the six AND-OR units into one system as seen in Fig. 2. The AND-OR units are now fixed and the *Selectors* are to be evolved in the assembled system. Which outputs, from each of the AND-OR units, to select for making the *total* performance highest possible are now determined. Thus, the fitness is measured using the same training set as in step 1 but the evaluation is now on the output of the Max Selector.

- 3. The system is now ready to be applied in the prosthesis.

In the first step, subsystems are evolved separately, while in the second step these are evolved together. The motivation for evolving separate subsystems – instead of a single system in one operation, is that earlier work has shown that the evolution time can be substantially reduced by this approach [12,13]. In this paper, a less flexible AND-OR unit is used rather than the more general multi-layer gate array used in the earlier works. This is due to the initial experiments indicated that this restriction of flexibility was beneficial to make GA easier find better performing circuits. This is reasonable since only the connections are represented in the chromosome. In the architecture used earlier, the function of each gate was included as well.

This first step of evolution corresponds to the partitioned training vector approach presented in Section 3.1. In the following experiments, evolving subsystems, as described above, are compared to evolving a system directly. In the latter case, the system is evolved in one operation to classify all the six motions in the training set. The system consists of only one AND-OR unit with one gate output for each motion.

The layers of AND and OR gates in one AND-OR unit consist of 32 gates each. This number has been selected to give a chromosome string of about 1000 bits which has been shown earlier to be appropriate for GA. A larger number would have been beneficial for expressing more complex Boolean functions. However, the search space for GA could easily become too large. For the step 1 evolution, each gate's *inputs* are determined by evolution. The encoding of each gate in the binary chromosome string is as follows:

As described in the previous section, the EMG signal input consists of 16 bits. Inverted versions of these are made available on the inputs as well, making up a total of 32 input lines to the gate array. The evolution will be based on gate level. However, since several output bits are used to represent one motion, the signal resolution becomes increased from the two binary levels.

For the step 2 evolution, each line in each selector is represented by *one* bit in the chromosome. If a bit is "0", the corresponding line should *not* be input to the counter, whereas if the bit "1", the line *should* be input.

#### 3.3 Fitness Function

The fitness function is important for the performance of GA in evolving circuits. For the step 1 evolution, the fitness function – applied for each AND-OR unit separately, is as follows for the motion m ( $m \in [0, 5]$ ) unit:

$$F_1(m) = \frac{1}{s} \sum_{j=0}^{50m-1} \sum_{i=1}^{O} x + \sum_{j=50m}^{50m+49} \sum_{i=1}^{O} x + \frac{1}{s} \sum_{j=50m+50}^{P-1} \sum_{i=1}^{O} x$$

where  $x = \begin{cases} 0 \text{ if } y_{i,j} \neq d_{m,j} \\ 1 \text{ if } y_{i,j} = d_{m,j} \end{cases}$

where  $y_{i,j}$  in the computed output of OR gate i and  $d_{m,j}$  is the corresponding target value of the training vector j. P is the total number of vectors in the training set (P = 300). As mentioned earlier, each subsystem is trained for one motion. This includes outputting "0" for input vectors for other motions.

The s is a scaling factor to implicit emphasize on the vectors for the motion the given subsystem is assigned to detect. An appropriate value (s = 4) was found after some initial experiments. The O is the number of outputs included in the fitness function and is either 16 or 32 in the following experiments (referred to as "fitness measure" in the result section).

The fitness function for the step 2 evolution is applied on the complete system and is given as follows:

$$F_2 = \sum_{j=0}^{P-1} x \text{ where } x = \begin{cases} 1 \text{ if } d_{m,j} = 1 \text{ and } m = i \text{ for which } \max_{i=0}^{5} (Counter_i) \\ 0 \text{ else} \end{cases}$$

This fitness function counts the number of training vectors for which the target  $output^1$  being "1" equals the id of the counter having the maximum output.

#### 3.4 The GA Simulation

Various experiments were undertaken to find appropriate GA parameters. The ones that seemed to give the best results were selected and fixed for all the experiments. This was necessary due to the large number of experiments that would have been required if GA parameters should be able vary through all the experiments. The preliminary experiments indicated that the parameter setting was not a major critical issue.

The simple GA style – given by Goldberg [15], was applied for the evolution with a population size of 50. For each new generation an entirely new population of individuals is generated. Elitism is used, thus, the best individuals from each generation are carried over to the next generation. The (single point) crossover rate is 0.8, thus the cloning rate is 0.2. Roulette wheel selection scheme is applied. The mutation rate – the probability of bit inversion for each bit in the binary chromosome string, is 0.01.

The proposed architecture fits into most FPGAs. The evolution is undertaken off-line using software simulation. However, since no feed-back connections are used and the number of gates between the input and output is limited to n, the real performance should equal the simulation. Any spikes could be removed using registers in the circuit.

For each experiment presented in the next section, four different runs of GA were performed. Thus, *each* of the four resulting circuits from step 1 evolution is taken to step 2 evolution and evolved for four runs.

As mentioned earlier only *one* output bit is "1" for each training vector.

#### 4 Results

This section reports the experiments undertaken to search for an optimal configuration of the prosthetic hand controller. They will be targeted at obtaining the best possible performance for the test set.

| Table | 1. | The | results | of | evolving | the | prosthetic | hand | ${\rm controller}$ | in | ${\it several}$ | different |

|-------|----|-----|---------|----|----------|-----|------------|------|--------------------|----|-----------------|-----------|

| ways. |    |     |         |    |          |     |            |      |                    |    |                 |           |

| Type of system                | # inp/gate | Step 1 evolution |      |      | Step 1+2 evolution |       |      |  |

|-------------------------------|------------|------------------|------|------|--------------------|-------|------|--|

|                               |            | Min              | Max  | Avr  | Min                | Max   | Avr  |  |

| A: Fitness measure 16 (train) | 3          | 63.7             | 69.7 | 65.5 | 71.33              | 76.33 | 73.1 |  |

| A: Fitness measure 16 (test)  | 3          | 50.3             | 60.7 | 55.7 | 44                 | 67    | 55.1 |  |

| B: Fitness measure 32 (train) | 3          | 51               | 57.7 | 53.4 | 70                 | 76    | 72.9 |  |

| B: Fitness measure 32 (test)  | 3          | 40               | 46.7 | 44.4 | 45                 | 54.3  | 50.1 |  |

| C: Fitness measure 16 (train) | 2          | 51.3             | 60.7 | 54.8 | 64.3               | 71.3  | 67.5 |  |

| C: Fitness measure 16 (test)  | 2          | 46               | 51.7 | 49   | 44.3               | 54.7  | 50   |  |

| D: Fitness measure 16 (train) | 4          | 59.3             | 71.3 | 65.5 | 70                 | 76    | 73.4 |  |

| D: Fitness measure 16 (test)  | 4          | 52.7             | 59.7 | 55.3 | 48.3               | 56.3  | 52.7 |  |

| E: Direct evolution (train)   | 4          | 56.7             | 63.3 | 59.3 | -                  | -     | -    |  |

| E: Direct evolution (test)    | 4          | 32.7             | 43.7 | 36.6 | -                  | -     | -    |  |

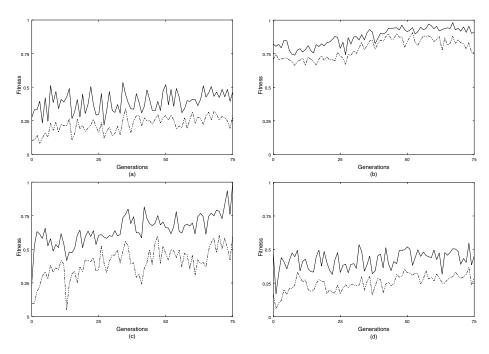

Table 1 shows the main results – in percentage correct classification. Several different ways of evolving the controller are included. The training set and test set performances are listed on separate lines in the table. The *fitness measure* – introduced in Section 3.3, will be discussed later in this section. The "# inp/gate" column includes the number of inputs for each gate in the AND-OR unit. The columns beneath "Step 1 evolution" report the performance after only the *first* step of evolution. That is, each subsystem is evolved separately, and afterwards they become assembled to compute their total performance. The "Step 1+2 evolution" columns show the performance when the *selector units* have been evolved too (step 2 of evolution). In average, there is an improvement in the performance for the latter. Thus, the proposed *increased complexity evolution* give rise to improved performances.

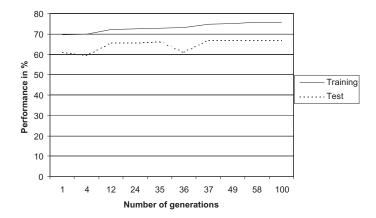

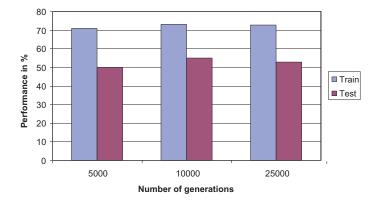

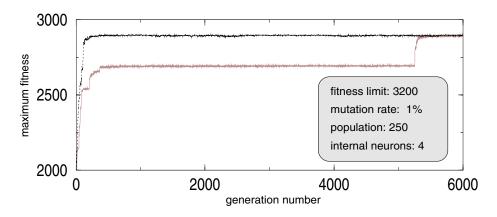

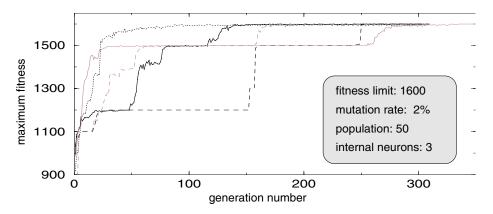

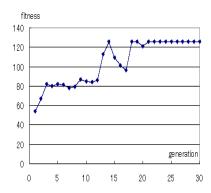

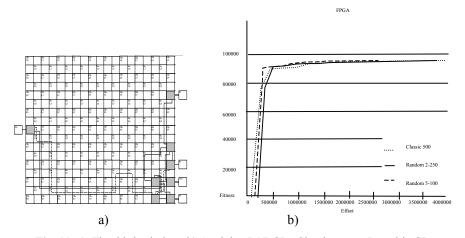

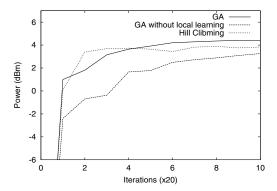

In total, the best way of evolving the controller is the one listed first in the table. The circuit evolved with the best test set performance obtained 67% correct classification. Fig. 3 shows the step 2 evolution of this circuit. The training set performance is monotone increasing which is demanded by the fitness function. The test set performance is increasing with a couple of valleys. The circuit had a 60.7% test set performance after step 1 evolution<sup>2</sup>. Thus, the step 2 evolution provides a substantial increase up to 67%. Other circuits didn't perform that well, but the important issue is that it has been shown that the proposed architecture provides the potential for achieving high degree of generalization.

<sup>&</sup>lt;sup>2</sup> Evaluated with all 32 outputs of the subsystems.

Fig. 3. Plot of the step 2 evolution of the best performing circuit.

The results presented in this paper are from the first experiments undertaken. A lot more should be conducted to optimize parameters as well determining how to measure the fitness during evolution to secure a high test set performance in general.

A feed-forward neural network was trained and tested with the same data sets. The network consisted of (two weight layers with) 16 inputs, 40 hidden units and 6 outputs. In the best case, a test set performance of 58.8% correct classification was obtained. The training set performance was 88%. Thus, a higher training set performance but a lower test set performance than for the best EHW circuit. This shows that the EHW architecture holds good generalisation properties.

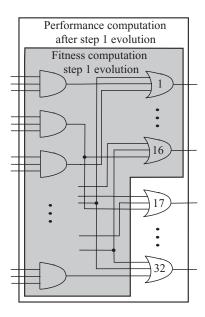

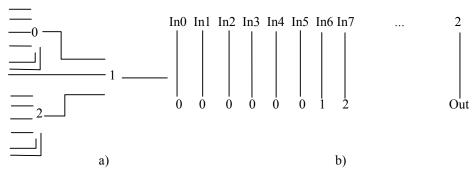

The experiment B is the same as A except that in B all 32 outputs of each AND-OR unit are used to compute the fitness function in the step 1 evolution. In A, each AND-OR unit also has 32 outputs but only 16 are included in the computation of the fitness function, see Fig. 4. The 16 outputs not used are included in the chromosome and have random values. That is, their value do not affect the fitness of the circuit. What is amazing about this is that the performance of A in the table for the step 1 evolution is computed by using all the 32 outputs. Thus, over 10% better training set as well as the test set performance (in average) are obtained by having 16 outputs "floating" rather than measuring their fitness during the evolution!

What is also interesting is that if the performance of the circuits in A is measured (after step 1 evolution) with only 16 outputs, the performance is not very impressive. Thus, "floating" outputs in the evolution substantially improve the performance – including the test set performance.

This may seem strange but has a reasonable explanation. Only the OR gates in the AND-OR unit are "floating" during the evolution since all AND gates may be inputs to the 16 OR gates used by the fitness function. The 16 "floating" OR-gates then provide additional combination of these *trained* AND gates. To

Fig. 4. A "fitness measure" equal to 16.

explain why not B shows better performance, the description in Section 3.1 is appropriate. In this experiment, the chromosome is longer since in A the bits assigned to the 16 "floating" OR-gates are not used. Other numbers of "floating" OR gates (8 and 24) were tested but the results were best for 16.

A further improvement of A could be by introducing one *more* step of evolution. After finishing step 1 evolution, the AND-gates and the OR-gates covered by the fitness function  $F_1$  could be fixed, and a new step of evolution could evolve the 16 "floating" OR gates. This could increase the performance, but not necessarily, since the step 2 evolution already removes the bad performing OR gates.

The C and D rows in the table contain the results when the gates in the AND-OR units each consists of two and four inputs, respectively. The lowest figures are for two input gates indicating that the architecture is too small to represent the given problem. Four inputs, on the other hand, could be too complex since having *three* input gates give a slightly better results.

Each subsystem is evolved for 10,000 generations each, whereas the step 2 evolution was applied for 100 generation. These numbers were selected after a number of experiments. One comparison of the step 1 evolution (each gate having three inputs) is included in Figure 5 and shows that the best average performance is achieved when evolving for 10,000 generations.

The circuits evolved with direct evolution (E) were undertaken for 100,000 generations<sup>3</sup>. The training set performance is impressive when thinking of the

$<sup>^{3}</sup>$  This is more than six times 10,000 which were used in the other experiments.

Fig. 5. Performance of three different numbers of generations in step 1 evolution (average of four runs).

simple circuit used. Each motion is controlled by a *single* four input OR gate. However, the test set performance is very much lower than what is achieved by the other approaches. This is explained by having an architecture that is too small to provide good generalization. A larger one, on the other hand, would make the chromosome string longer with the problems introduced in Section 3.1. This once again emphasizes the importance of applying the *increased complexity evolution* scheme.

An interesting observation in the experiments is that the number of inputs to a gate is not always equal to the preselected value. Several inputs to *one* gate can be connected to the same source and thus, reducing the number of active inputs. Further, both inverted and non-inverted version of the same signal can be input to an AND gate. This makes the output becoming fixed to "0" and the OR gates connecting to it would then "reduce" its number of inputs. Such behavior illustrates the good adaptivity features within the AND-OR units.

According to these results there are several interesting topics for future work. The step 2 evolution could include a selection of *subsystem* for each motion *in addition* to the selector parameters. That is, for each motion a *set* of separately evolved subsystems could be available for the step 2 evolution to select among. In this way you would be able to assemble the best combination of many of the subsystems evolved in the step 1 evolution, rather than only six. Further, the architecture is a general one and should be applied to other problems within pattern recognition/classification.

#### 5 Conclusions

In this paper, a new EHW architecture for pattern classification including incremental evolution has been proposed. The best circuit evolved shows a better generalization performance that what was obtained by artificial neural networks.

The results illustrate that this is a promising approach to evolving systems for complex real-world applications.

#### Acknowledgments

The author would like to thank the group leader Dr. Higuchi and the researchers in the Evolvable Systems Laboratory, Electrotechnical Laboratory, Japan for inspiring discussions and fruitful comments on my work, during my visit there in January-April 2000. Further, I will express my gratefulness to the Japan Science and Technology Corporation (JST) for awarding me the STA fellowship making the visit possible.

#### References

- R.N. Scott and P.A. Parker. Myoelectric prostheses: State of the art. J. Med. Eng. Technol., 12:143–151, 1988.

- S. Fuji. Development of prosthetic hand using adaptable control method for human characteristics. In Proc. of Fifth International Conference on Intelligent Autonomous Systems., pages 360–367, 1998.

- I. Kajitani and other. An evolvable hardware chip and its application as a multifunction prosthetic hand controller. In Proc. of 16th National Conference on Artificial Intelligence (AAAI-99), 1999.

- 4. W-P. Lee et al. Learning complex robot behaviours by evolutionary computing with task decomposition. In Andreas Brink and John Demiris, editors, *Learning Robots: Proc. of 6th European Workshop, EWLR-6 Brighton.* Springer, 1997.

- X. Yao and T. Higuchi. Promises and challenges of evolvable hardware. In T. Higuchi et al., editors, Evolvable Systems: From Biology to Hardware. First Int. Conf., ICES 96. Springer-Verlag, 1997. Lecture Notes in Computer Science, vol. 1259.

- E. Cantu-Paz. A survey of parallel genetic algorithms. Calculateurs Parallels, 10(2), 1998. Paris: Hermes.

- 7. M. Iwata et al. A pattern recognition system using evolvable hardware. In *Proc. of Parallel Problem Solving from Nature IV (PPSN IV)*. Springer Verlag, September 1996. Lecture Notes in Computer Science, vol. 1141.

- 8. P. Haddow and G. Tufte. An evolvable hardware FPGA for adaptive hardware. In *Proc. of Congress on Evolutionary Computation*, 2000.

- 9. M. Murakawa et al. Hardware evolution at function level. In *Proc. of Parallel Problem Solving from Nature IV (PPSNIV)*. Springer Verlag, September 1996. Lecture Notes in Computer Science, vol. 1141.

- J. R. Koza. Genetic Programming II: Automatic Discovery of Reusable Programs. The MIT Press, 1994.

- 11. W.D. Hillis. Co-evolving parasites improve simulated evolution as an optimization procedure. In *Physica D*, volume 42, pages 228–234. 1990.

- 12. J. Torresen. Scalable evolvable hardware applied to road image recognition. In *Proc. of the 2nd NASA/DoD Workshop on Evolvable Hardware*. Silicon Valley, USA, July 2000.

- 13. J. Torresen. A divide-and-conquer approach to evolvable hardware. In M. Sipper et al., editors, *Evolvable Systems: From Biology to Hardware. Second Int. Conf.*, *ICES 98*, pages 57–65. Springer-Verlag, 1998. Lecture Notes in Computer Science, vol. 1478.

- 14. M. Yasunaga et al. Genetic algorithm-based design methodology for pattern recognition hardware. In J. Miller et al., editors, *Evolvable Systems: From Biology to Hardware. Third Int. Conf.*, *ICES 98.* Springer-Verlag, 2000. Lecture Notes in Computer Science, vol. 1801.

- 15. D. Goldberg. Genetic Algorithms in search, optimization, and machine learning. Addison Wesley, 1989.

# Untidy Evolution: Evolving Messy Gates for Fault Tolerance

Julian F. Miller<sup>1</sup> and Morten Hartmann<sup>2,3</sup>

School of Computer Science, University of Birmingham,

Birmingham B15 2TT, UK,

j.miller@cs.bham.ac.uk

Department of Computer and Information Science,

The Norwegian University of Science and Technology,

7491 Trondheim, Norway,

Morten.Hartmann@idi.ntnu.no

Abstract. The exploitation of the physical characteristics has already been demonstrated in the intrinsic evolution of electronic circuits. This paper is an initial attempt at creating a world in which "physics" can be exploited in simulation. As a starting point we investigate a model of gate-like components with added noise. We refer to this as a kind of messiness. The principal idea behind these messy gates is that artificial evolution makes a virtue of the untidiness. We are ultimately trying to study the question: What kind of components should we use in artificial evolution? Several experiments are described that show that the messy circuits have a natural robustness to noise, as well as an implicit fault-tolerance. In addition, it was relatively easy for evolution to generate novel circuits that were surprisingly efficient.

#### 1 Introduction

Natural evolution has produced the most subtle and complex bio-chemical information processing machines known (i.e. living creatures). In addition to this complexity living systems possess a remarkable degree of fault tolerance and robustness. At this point it is necessary to clarify the exact meanings of the terms: fault-tolerance and robustness. Robustness deals primarily with problems that are expected to occur and must be protected against. By contrast, fault tolerance primarily deals with problems that are unexpected. Humans can design systems to be robust but true fault tolerance is a much more difficult problem[1, 19]. This is particularly acute in digital electronics. Digital gates are robust from the point of view of minor changes in input voltages but systems built from them are fragile to stuck-at faults.

Another aspect of human designed systems is that they are usually built from production line components (especially if they are electronic). Living systems are built from components (i.e. cells) that vary considerably in their properties. It is now recog-

<sup>&</sup>lt;sup>3</sup> The work was carried out while in the School of Computer Science, University of Birmingham.

Y. Liu et al. (Eds.): ICES 2001, LNCS 2210, pp. 14-25, 2001.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2001

nised that many of the advantageous properties of living systems emerge from the way in which the individual properties of the components are exploited.

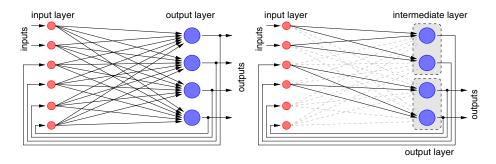

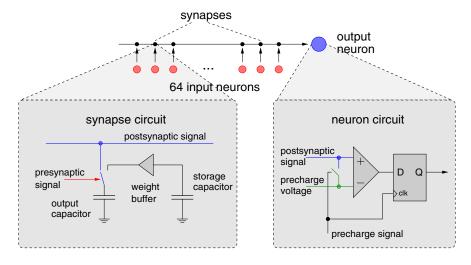

Artificial neural networks (ANN) were one of the first bio-inspired circuits to be developed. It has been suggested that ANNs exhibit graceful degradation in the presence of faults [2]. However more recent work has indicated that ANNs are not intrinsically fault tolerant [9,15].

In recent decades the use of design algorithms that employ the principles of Darwinian evolution have been applied to the design of electronic systems [3,7,16,17]. Such work has become known as Evolvable Hardware. Already researchers are using bio-inspired ideas to design electronic hardware with more fault-tolerance [4,10]. One of the most intriguing findings in this field is that of Adrian Thompson [11]. He showed that it was possible for artificial evolution to create FGPA designs that exploited the physical characteristics of the silicon substrate to efficiently carry out a particular task. Thompson found that unconstrained artificial evolution explored very unusual ways of solving problems *precisely* because it was able to exploit the subtle and incidental physical characteristics. It can be argued that evolution has produced such complex systems because it can make use of the full, *unmodellable* richness of the physical world.

Another question raised from Thompson's work is the following: What basic components should we be using in artificial evolution? It does not seem very likely that the electronic components that have been created for human design should happen to be particularly useful in artificial evolution. Indeed it could be seen as a testament to the power of evolution that using them, artificial evolution could produce anything useful at all. If one is going to build practical systems using artificial evolution it appears that one has to go back to basics and try to design radically new forms of electronic components, or use existing components in novel configurations [e.g. 18] that might assist the artificial evolutionary process. This could be done in two ways. First, one could search for special materials and then subject them to intrinsic artificial evolution, and second, one could try to define new kinds of components in simulation and subject them to extrinsic evolution. The former is obviously a good approach, however it is potentially very expensive and likely to be very difficult. The latter though, perhaps, is not as exciting, however it is feasible and could actually assist the former goal by helping us to identify what kinds of properties are important. These thoughts were the starting point for the work reported in this paper.

The paper is divided as follows: Section 2 is concerned with the definition of the new component model (which is described as *messy*). Section 3 describes the genotype representation and evolutionary algorithm that was used. Section 4 describes the experiments performed. In section 5 the experimental results are presented. In section 6 the concluding remarks are made. The paper finishes with a description of possible future work in section 7.

#### 2 Messy gates

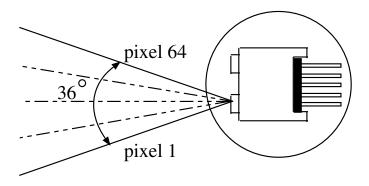

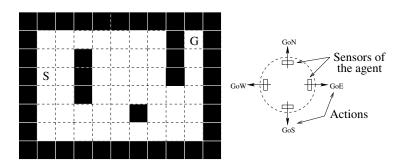

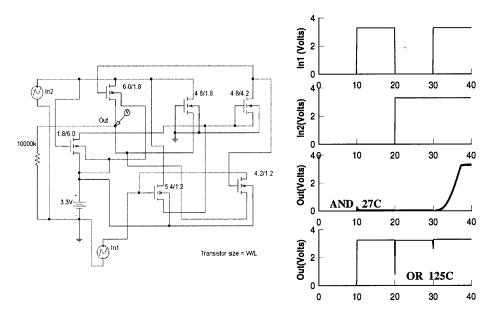

Since the aim is not only to create new types of components for use in artificial evolution but also to *understand* exactly how they work, it was necessary to choose a new model that was adjustable. It was desirable to be able to change a parameter continuously so that the new component model could become the same as a familiar traditional component. A natural choice of traditional component was a digital logic gate. Accordingly, a model that was that of a digital multiplexer with additional randomness on the output was created. The new model took real valued input combined the inputs to give a real valued output. Random noise was then superimposed on the output (figure 1). These gates are being referred to as *messy* and as having a degree of *messiness*.

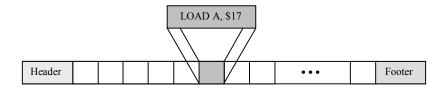

Fig. 1. Model of messy MUX

The equation below describes the messy MUX:

$$y = mr + a\overline{c} + bc . (1)$$

where m represents the constant value of messiness chosen for the entire circuit and r represents a real random number uniformly sampled from the interval [-1.0, 1.0]. The inputs to the messy MUX are a and b, and c is the control input. The bar over c refers to l-c. All variables are real-valued. Clearly when m=0 and a, b, and c are only allowed to be 0 or 1, the digital MUX is recovered and all the rules of Boolean logic apply. In the experiments a messy MUX with one input inverted (input b would then become b-b) was used as well. Once real values for variables are allowed it is not clear how to decide real-valued equivalence of the Boolean operators. Arithmetic add and multiply are the closest analogues of the inclusive-OR and the AND operators. The model we have used was not designed to be a feasible electronic model, since the primary aim was to investigate the ability of artificial evolution to use any chosen model. No claims are made about the "correctness" of the model we used other than it possessed the property of being a superset of the digital case. Now that the system is designed, more complex and physically realistic models can easily be added later (even though it may be hard to design the model itself).

### 3 Evolutionary algorithm and genotype

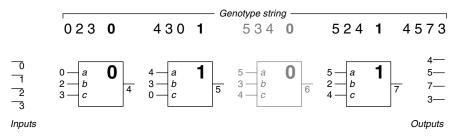

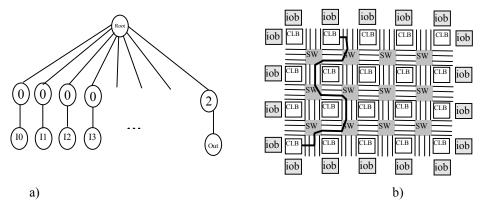

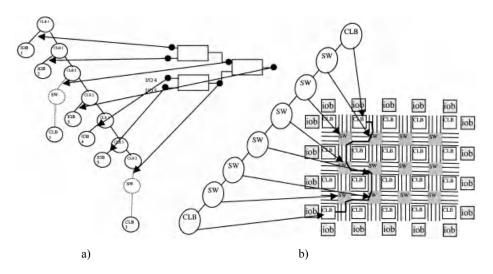

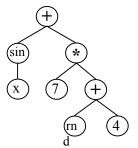

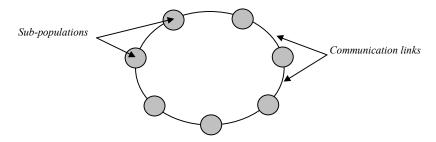

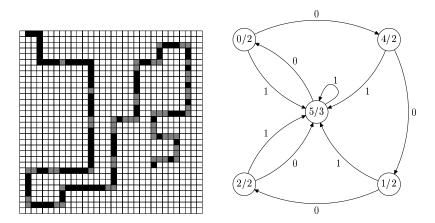

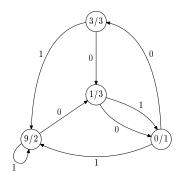

The genotype representation is the same as that used for evolving digital designs [5,6]. It is best explained with a small example. In figure 2 are shown four messy MUX (mMUX) gates. The numbers (0-3) refer to the four primary inputs of the target function. The numbers on the inputs to the mMUX refer to the connections to the primary

inputs or the outputs of other mMUX. The outputs of the mMUX are labeled (sequentially following on from the inputs). Thus the second mMUX on the left has the "a" input connected to the output of the first mMUX, the other two mMUX inputs are connected to the two primary inputs 3 and 0. In this example it is assumed that the target function has four outputs. Thus the genotype has four output connections (4 5 7 3). The numbers in bold refer to which of the two mMUX were being used (0 refers to mMUX with no inputs inverted, 1 refers to the "b" input being inverted). The numbers printed in grey refer to inactive genes or mMUX (i.e the third mMUX does not have its output connected). This paper only considers feed-forward circuits. The representation allows any mMUX to have its input connected to any other mMUX on its left.

Fig. 2. Example genotype and resulting circuit with four inputs and four outputs

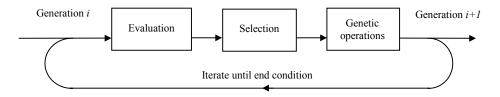

The evolutionary algorithm employed was a simple form of (1+4) evolutionary strategy (ES). In this case a population of 5 random chromosomes is randomly generated and the fittest chromosome selected. The new population is then filled with mutated versions of this. Random mutation is defined as a percentage of genes in the population that were mutated. The mutation operator respects the feed-forward nature of the circuits and also the different alphabets associated with connections and functions.

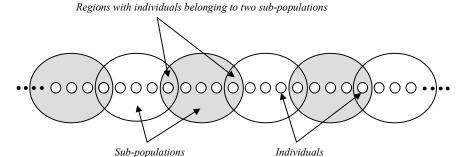

Each *circuit* has a fixed value of messiness m. However each gate has its own random value r (equation 1). This is illustrated in figure 3.

Fig. 3. Circuit schematic with individual random values

The fitness of an individual is measured by testing the chromosome with all possible combinations of inputs and comparing the output values with the target Boolean truth table. For all experiments described in this paper, the target is a 2-bit multiplier. Thus, there are 4 inputs, 4 outputs and  $2^4$  possible input test vectors yielding a total of 64 output bits in the truth table.

Fitness is equal to the number of output bits of a circuit being equal to the corresponding bit in the target truth table. This is referred to as bitwise correctness. A perfectly functional circuit would have all its output bits equal to the output bits of the truth table, and thus the bitwise correctness would equal 64 in the case of the 2-bit

multiplier. In the case of messy circuits, the real valued internal signals were rounded at the output before being compared to the target truth table.

#### 4 Experiments

Several experiments were performed to investigate the nature of the mMUX and its influence on the evolved circuits and the evolutionary algorithm. These experiments are described below.

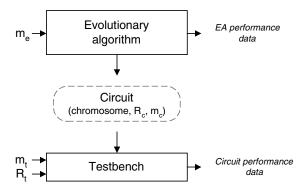

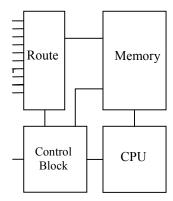

Fig. 4. Experimental setup

The setup for the experiments is shown in figure 4. The evolutionary algorithm produces a circuit consisting of a chromosome, a set of random values  $R_c$  and the messiness used ( $m_c$ = $m_e$ ). A test bench allows measuring the performance of a circuit by using different values of messiness ( $m_t$ ), different sets of random values ( $R_t$ ) and introducing stuck-at faults.

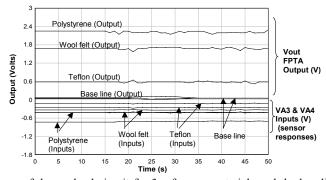

The first two experiments investigated whether it was feasible to evolve circuits that exhibited a natural robustness to internal random noise within some specified range.

A set of about 500 chromosomes was evolved for six different values of m. The fitness measure was based on taking an average of the bitwise correctness over 15 sets of random values r (for each gate). Evolution was halted each time the fitness was equal to 64 (all 15 chromsomes had bitwise correctness equal to 64). This set of chromosomes was used to generate the results of the first three experiments. Thus, these experiments investigate different configurations of the testbench, with the fitness of each circuit measured as an average over 50 trials. This was done both to introduce new random values  $R_t$  for every test performed, as well as testing different randomly chosen gates for stuck-at faults in the case of the third experiment.

#### 4.1 First experiment

The first experiment sought to investigate how computationally demanding it is to evolve circuits with high values of m, as well as the general performance of the circuits in an environment equally noisy to the one in which it was evolved ( $m_t=m_c$ ). In all other respects the experiment was the same as that described previously.

#### 4.2 Second experiment

Thompson has demonstrated that it is possible to evolve robust circuits intrinsically by exposing them to various environments [12, 13]. In the second experiment, the same set of chromosomes was tested with the messiness of the test bench  $m_t$ , being set to increasingly higher values. This simulates the circuits running in increasingly more noisy environments, and disregards whatever value  $m_e$  used when the chromosomes were evolved. This was done to investigate the robustness of the chromosomes with regards to the amplification  $m_t$  of the internal noise, and its relation to the value of  $m_e$  used in the evolution of the different chromosomes.

#### 4.3 Third experiment

An interesting property of a digital circuit is its fault tolerance. An experiment was carried out to measure the tolerance in the evolved circuits to stuck-at faults.

The test bench was set up to subject the circuits to stuck-at-1 faults. Stuck-at-1 faults were selected since their impact on a multiplier is on average more severe then stuck-at-zero faults. This is due to the fact that the output part of the 2-bit multiplier truth table contains 14 zeros and 50 ones. Thus, increasing numbers of stuck-at-0 faults force the bitwise correctness towards 50. On the other hand, increasing the numbers of stuck-at-1 faults force the bitwise correctness towards 14.

#### 4.4 Fourth experiment

The last experiment sought to investigate how evolution would be capable of exploiting individual characteristics of given gates. This was done by generating random values for  $R_{\rm e}$  for each gate only once for each run of the evolutionary algorithm. The algorithm would then try to utilize the properties of each individual mMUX in the circuit to solve the problem.

The set of random values was saved with each chromosome as  $R_c$ , and the test bench was configured to use the saved random values as the values to be used under test ( $R_t$ = $R_c$ ).

The fitness function was modified by adding the number of redundant nodes to the bitwise correctness (provided the bitwise correctness equalled 64). This was done to investigate if it would be possible to evolve smaller circuits for higher values of m.

#### 5 Results

This section presents the results obtained through the experiments carried out in section 4. The results are briefly discussed within the limits of the scope of this paper.

#### 5.1 First experiment

Evolving chromosomes with bitwise correctness equal to 64 was more computationally expensive for large values of m. Purely digital circuits (m=0) took an average of 2000 generations to evolve. On the other hand, it required an average of more than 30000 generations to evolve circuits with a messiness value of m=0.25.

Even though all chromosomes are evaluated 15 times to distribute the random values creating noise at the gate outputs, the same chromosome may not obtain perfect fitness if a new set of random values are introduced. In such a way, the number of evaluations during evolution can be considered a choice between computational effort and robustness of the evolved circuit (with regards to random values introduced).

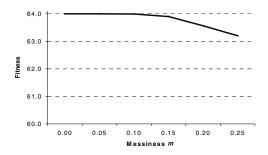

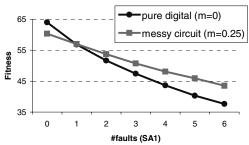

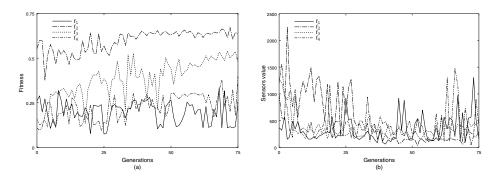

The resulting average fitness is shown in figure 5.

Fig. 5. Average fitness measured through tests

Even though this figure shows a negative trend, it implies that messy circuits are pretty robust to variations in the internal noise within the range  $m_e$  used when the particular circuit was evolved, as the drop in fitness was quite small.

Finally, this experiment revealed another property of evolving messy circuits. Figure 6 illustrates how chromosomes evolved with high values of m tend to produce smaller circuits then those produced when messiness is low. This is probably due to the fact that evolution finds a way to reduce the amount of noise the circuit is exposed to. Each new gate means a new noisy value to cope with.

**Fig. 6.** The number of gates tend to be small for larger values of m

#### 5.2 Second experiment

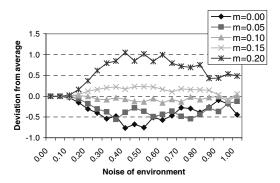

When the evolved circuits were tested in increasingly more noisy environments, a clear trend showed increased robustness for circuits evolved with higher messiness (m<sub>e</sub>). This trend is shown in figure 7. The graph shows the deviation from the average fitness over all evolved circuits, when exposed to increasing noise in the environment.

Fig. 7. Average fitness when exposed to more noisy environments

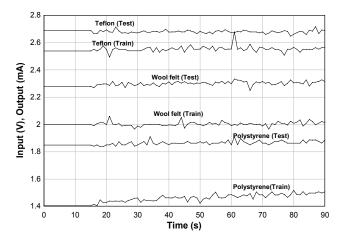

#### 5.3 Third experiment

It was difficult to see any clear trend on whether messy circuits were more tolerant then pure digital ones when they used a small number of gates. It was desirable to investigate whether larger circuits with high messiness would be more fault tolerant. To reliably obtain large circuits (using the maximum number of gates =30) a term had to be added to the fitness that favoured larger circuits. This meant that circuits without

a bitwise correctness of 64 had to be accepted. However it was observed that these circuits proved to be largely more fault-tolerant to the stuck-at-1 faults and showed a more graceful degradation when compared to the zero messiness case. This trend is shown in the graph in figure 8. Note that the test bench in this case introduced the faults in the same environment that each chromosome was originally evolved (same value of m). So the circuits had to cope with intrinsic randomness associated with the messiness  $m_c$ , in addition to the introduced faults.

Fig. 8. Difference in degradation of large circuits

An interesting aspect of this graceful degradation is the fact that this tolerance is implicit, since these circuits were never evolved explicitly with fault tolerance to stuck-at faults as a part of the EA. A comparison of the fault tolerance of the evolved digital case (m=0) and conventional circuits was not carried out. However, certain evolutionary systems may inhibit natural mutation tolerance due to the workings of the evolutionary process [14]. Such tolerance is unlikely to have any effect on the EA used in this paper, as a result of the steep hill-climbing nature of the algorithm.

The results where compared to circuits evolved explicitly for fault tolerance (i.e. tolerance to stuck-at fault was included in the fitness function). This comparison showed that explicit fault tolerance could be evolved to display stronger tolerance, but at a higher computational cost.

#### 5.4 Fourth experiment

The fourth experiment revealed that evolving circuits with permanent sets of values  $R_{\rm c}$  for each chromosome, was slightly more computationally demanding for higher values of m.

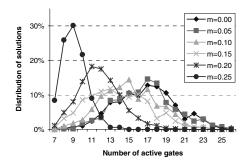

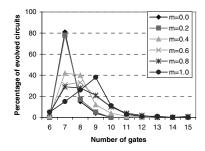

Figure 9 shows the percentage of evolved circuits having a particular number of gates for various messiness values. The low values of m tended to yield circuits with 7 gates, higher values of m had a wider distribution of evolved circuits.

Fig. 9. Distribution of solutions with regards to the number of gates in the evolved circuits

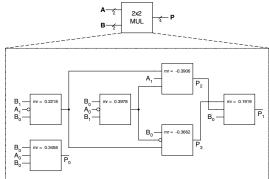

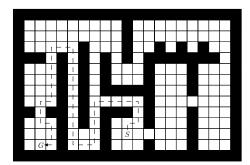

For increasing values of m, a larger amount of the evolved circuits consisted of only six gates, suggesting that only sets of random values with sufficient range allow such small circuit. The small circuits are interesting, since it appears the minimum number of gates (of the two types of multiplexers used) that can be used to solve the problem in a pure digital manner is 7 [6]. An example of a circuit of this type is shown in figure 10. A and B are the two 2-bit numbers being multiplied, while P is the output product. Subscripts on the inputs and outputs refers to the significance of the bits (0 being least significant). A circle at an input illustrates an inverted value. The shown circuit was evolved with m equal to 0.4. It demonstrates the ability of a blind evolutionary process to exploit all the "physical characteristics" of the components. This is reminiscent of Thompson's findings in [13] where he found that robust evolved clocked digital circuits exploited glitches, even though these are shunned in conventional human design.

**Fig. 10.** Example of a small evolved circuit (m=0.4)

#### 6 Conclusions

In this paper a new model of a gate-like component with added random noise was used for initial investigations. The experiments carried out so far indicates that such

components are beneficial in several ways. Firstly the new gate-like models naturally offered a robustness to noise. Secondly circuits that were evolved using these messy components exhibited implicit fault tolerance. Finally experiments indicated that in creating a simulateable world, "physical" characteristics (intrinsic random values) could be exploited to create surprisingly efficient designs (the six mMUX 2-bit multiplier). Artificial evolution appears to be quite adept at exploiting such things. It is not easy to imagine a human design process that could exploit such random differences. One advantage of such a simulation is that it is possible to inspect every detail of the "physics". In addition all the designs are replicable and the functionality of the evolved circuit can be verified mathematically. It may be that one cannot design a model with sufficient richness to allow artificial evolution to find really innovative ways of building circuits. In these cases intrinsic evolution may be the only way forward. However this appears to require the use of conventional technology (i.e. FPGAs, programmable-logic). One way forward might be to deliberately disrupt the silicon (perhaps by radiation) in order to enrich the natural physics. Another approach would be to look for novel materials for intrinsic evolution (i.e. evolvable matter arrays [8]). It should also be noted that at present the algorithms that are used in artificial evolution are very far from the sophistication and complexity of real biological evolution processes.

#### 7 Future work

This paper is a preliminary study into an area that to the knowledge of the authors is relatively unexplored. The model of messiness discussed here is really just a starting point. It is likely that more complex models of components would be much more suitable in for use in an evolutionary design process, since the produced circuits would be closer to a real hardware implementation.

Further on, a study into the general principles on how evolution exploits properties of the underlying hardware would be interesting. This paper attempts to initiate thoughts directed at issues that could be important in a search for more suitable media for evolutionary systems.

#### References

- A. Aviziensis "Towards systematic design of fault-tolerant systems", IEEE Computer, vol. 30, pp. 51-58, 1997.

- 2. L.A. Belfore and B.W. Johnson. "The fault-tolerance of neural networks", The International Journal of Neural Networks Research and Applications 1, pp. 24-41 (Jan 1989).

- 3. T. Higuchi and M. Iwata (eds.). Proceedings of the 1<sup>st</sup> International Conference on Evolvable Systems: From Biology to Hardware, Lecture Notes in Computer Science (ICES96), Springer-Verlag, Berlin, vol. 1259, 1996.

- D. Keymeulen, R. Zebulum "Fault-Tolerant Evolvable Hardware Using Field-Programmable Transistor Arrays", in IEEE Transactions on Reliability, vol. 49, no. 3, 2000.

- J. F. Miller and P. Thomson. "Cartesian Genetic Programming", in R. Poli, W. Banzhaf, W.B. Langdon, J. F. Miller, P. Nordin, T. C. Fogarty (eds.), Third European Conference on Genetic Programming Edinburgh 2000 (EuroGP2000), Lecture Notes in Computer Science, vol. 1802, pp. 121-132, Springer-Verlag, Heidelberg, 2000.

- 6. J. F. Miller, D. Job, V.K. Vassilev. "Principles in the Evolutionary Design of Digital Circuits Part I", in W. Banzhaf (ed.), Genetic Programming and Evolvable Machines, Vol. 1, No. 1/2, Kluwer Academic Publishers, Netherlands, pp. 7 35, 2000.

- J. F. Miller, A. Thompson, P. Thomson, T. C. Fogarty (eds.). Proceedings of the 3<sup>rd</sup> International Conference on Evolvable Systems: From Biology to Hardware (ICES00), Lecture Notes in Computer Science, vol. 1801, Springer-Verlag, Berlin, 2000.

- 8. J. F. Miller, "Evolvable Hardware: Some directions for the Future", an invited talk at the 2<sup>nd</sup> NASA/DOD Workshop on Evolvable Hardware, July 2000, available at http://ic-www.arc.nasa.gov/ic/eh2000/slides.html (last accessed 6-4-01)

- 9. J. Nijhuis, B. Hofflinger, A. Schaik and L. Spaanenburg. "Limits to Fault-Tolerance of a Feedforward Neural Network with Learning", Digest FTCS, pp. 228-235, June 1990.

- C. Ortega-Sanchez, D. Mange, S. Smith and A. Tyrrell "Embryonics: A Bio-Inspired Cellular Architecture with Fault Tolerant Properties", in W. Banzhaf (ed.), Genetic Programming and Evolvable Machines, Vol. 1, No. 3 Kluwer Academic Publishers, Netherlands, pp. 187 - 215, 2000.

- A. Thompson. "An evolved circuit, intrinsic in silicon, entwined with physics", in T. Higuch, M. Iwata, W. Liu (eds.), Proceedings of The 1<sup>st</sup> International Conference on Evolvable Systems: From Biology to Hardware (ICES96), Lecture Notes in Computer Science, vol. 1259, Springer-Verlag, Heidelberg, pp. 390 405, 1997

- 12. A. Thompson. "On the Automatic design of Robust Electronics through Artificial Evolution", in M. Sipper, D. Mange, A. Pérez-Uribe (eds.), Proceedings of The 2<sup>nd</sup> International Conference on Evolvable Systems: From Biology to Hardware (ICES96), Lecture Notes in Computer Science, vol. 1478, Springer-Verlag, Heidelberg, pp. 13- 24, 1998

- A. Thompson and P. Layzell. "Evolution on Robustness in an Electronics Design", in J. Miller, A. Thompson, P. Thomson, T.C. Fogarty (eds.), Proceedings of The 3rd International Conference on Evolvable Systems: From Biology to Hardware (ICES00), Lecture Notes in Computer Science, vol. 1801, Springer-Verlag, Heidelberg, pp. 218 - 228, 2000.

- A. Thompson. "Hardware Evolution Automatic Design of Electronic Circuits in Reconfigurable Hardware by Artificial Evolution", Springer-Verlag, London, 1998.

- B.E. Segee and M. J. Carter. "Fault Tolerance of Pruned Multilayer Networks", Digest IJCNN, pp. II-447-452, 1991.

- M. Sipper, E. Sanchez, D. Mange, M. Tomassini, A. Pérez-Uribe and A. Stauffer, "A phylogenetic, ontogenetic, and epigenetic view of bio-inspired hardware systems", IEEE Transactions on Evolutionary Computation vol. 1(1) pp.83-97, 1997.

- 17. M. Sipper, D. Mange and A. Pérez-Uribe (eds.). Proceedings of the 2<sup>nd</sup> International Conference on Evolvable Systems: From Biology to Hardware (ICES98), Lecture Notes in Computer Science, Springer-Verlag, Berlin, vol. 1478, 1998.

- 18. A. Stocia, D. Keymeulen, R. Zebulum, A. Thakoor, T. Daud, G. Klimeck, Y. Jin, R. Tawel and V. Duong. "Evolution of analog circuits on Field Programmable Transistor Arrays", in J. Lohn, A. Stocia, D. Keymeulen and S. Colombano, Proceedings of The 2nd NASA/DoD Workshop on Evolvable Hardware (EH'00), 2000, CA IEEE Computer Society Press.

- 19. R. White and F. Miles "Principles of fault-tolerance", in Proceedings of 11<sup>th</sup> Annual Conference on Applied Power Electronics, IEEE Press, vol. 1, pp. 18-25, 1996.

## **Evolutionary Design Calibration**

Thorsten Schnier and Xin Yao

School of Computer Science The University of Birmingham Edgbaston, Birmingham B15 2TT, UK {T.Schnier, X.Yao}@cs.bham.ac.uk

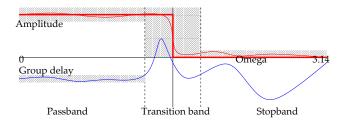

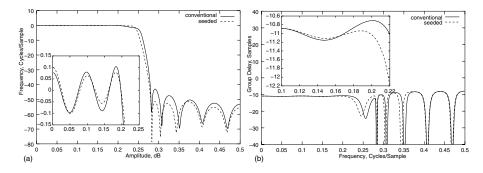

Abstract. Evolutionary methods are now beginning to be used routinely in design applications. However, even with computing speeds growing continuously, for many complex design problems evolutionary computing times are so long that their use is not practical. Divide and conquer based methods sometimes improve the situation, but in most cases the biggest speed improvement can be gained by adding domain knowledge. Combining evolutionary methods with conventional design methods is one way of doing this. This paper shows how evolutionary computation can be used to improve designs created by conventional design methods. A digital filter design problem is used to illustrate how a conventionally derived design can be further improved by evolutionary calibration. Our experimental results show that the evolutionary calibration algorithm is able to consistently improve the original designs by a considerable margin.

#### 1 Introduction

While evolutionary computation is able to create designs that are superior to conventionally derived designs (Yao 1999a, Schnier, Yao & Liu 2001), it sometimes does so at the expense of very long computation times. Introduction of domain knowledge is one of the major ways runtimes of evolutionary processes can be sped up. This can happen for example in the representation (Schnier & Yao 2000), selection, or genetic operators.

In digital filter design, there are existing conventional methods available for some classes of filters. In such cases, it make sense to use a hybrid approach, where the evolutionary algorithm (EA) is used to 'calibrate' a design created using a conventional design process.

#### 1.1 Limits of the Conventional Design Process

Designing digital filters, especially recursive filters, is not straightforward. For certain design problems with particular characteristics, it is possible to mathematically derive the optimal filter configuration; but in general, no such method exists. Instead, a number of approximation methods have to be developed, usually applicable only for a particular class of design problems.

Y. Liu et al. (Eds.): ICES 2001, LNCS 2210, pp. 26–37, 2001.

There are two limitations with this design method. First, for new problem classes, an approximation approach has to be developed first. For example, in Lu (1999), a process for designing stable IIR filters with equiripple passbands and peak-constrained least-squares stopbands is developed. As the title indicates, the class of filters that the method is applicable to is fairly limited. The development of the approximation requires special technical knowledge. This is different from evolutionary approaches, which can generally be used by non-specialists for larger classes of filter design problems.

The second limitation with the conventional design approach is that, depending on the exact approach taken, the resulting design can be a suboptimal because it follows a deterministic heuristic (or approximate) procedure. For example, the approach taken in Lu (1999) is based on iterative quadratic programming method with linearised constraints using a least-square objective. The resulting design may be suboptimal for three different reasons:

- Linearization of constraints: All constraints have to be formulated as linear inequalities. Constraints that are not initially linear have to be linearised. To ensure that the linearised constraint still excludes all designs that initially violated the constraint, it has to exclude some feasible designs (otherwise the linearised version would have to be identical to the original).

- Objective as a least-square problem: The objective has to be implemented as a weighted least-square function. Often, this is not exactly the same as the actual design goal. For example, in Lu (1999) the square error from the desired behaviour is used as the objective for the quadratic programming, but the maximum deviation from the desired behaviour is actually used to compare the final designs with other filter designs. While the maximum deviation is the 'real' design goal, the accumulated weighted square error is used for the design algorithm.

- The result of the iterated quadratic programming algorithm generally depends on the starting conditions. There is no guarantee of convergence to the global optimum (Lu 1999).

An evolutionary approach to digital filter design has been demonstrated in Schnier et al. (2001). The approach shows some success, but at the cost of a large computational effort. While the authors believe that the approach described in Schnier et al. (2001) can be improved and made more efficient, more reductions in computation time can be achieved by incorporating domain knowledge, whenever available, into the evolutionary design process.

For the design case studied in this paper, the starting point is the conventional design that was obtained through the existing conventional approach (Lu 1999) although the conventional approach can only find a suboptimal design. An EA will then be employed to calibrate the design and produced an improved design. The assumption is that by creating a hybrid approach where conventional design knowledge is combined with an evolutionary process, it is possible to generate results that are superior to the conventionally derived designs with an acceptable computational effort.

#### 1.2 Related Work

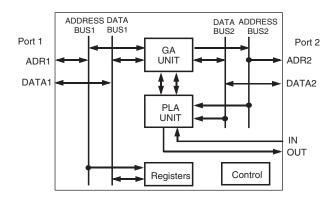

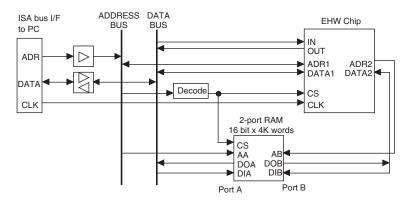

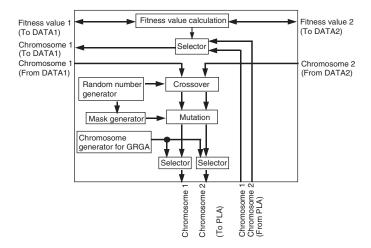

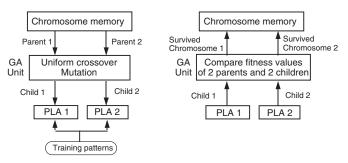

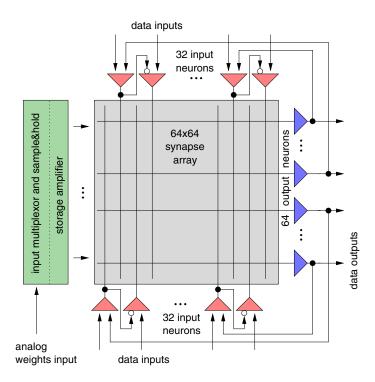

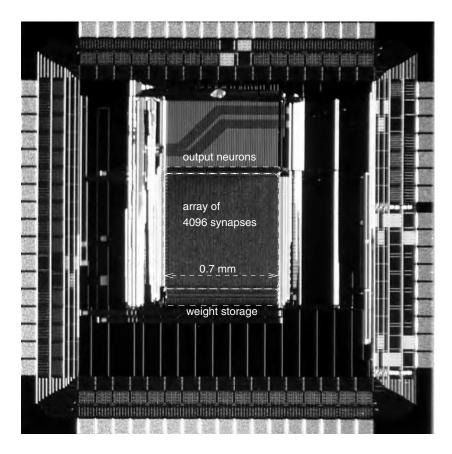

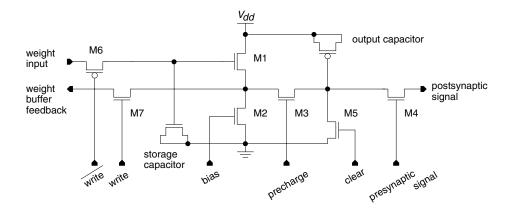

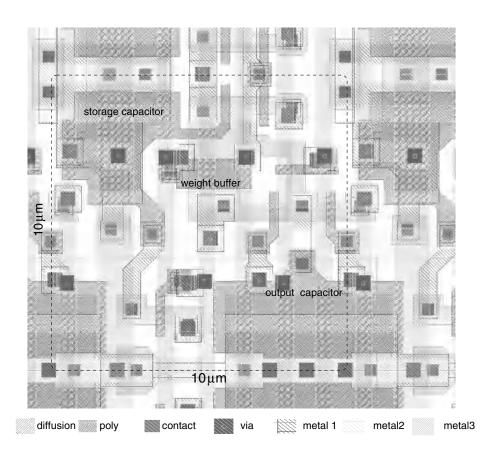

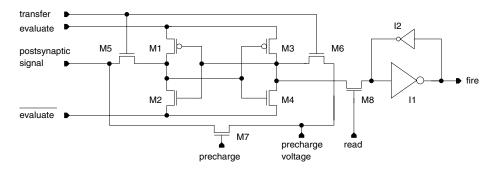

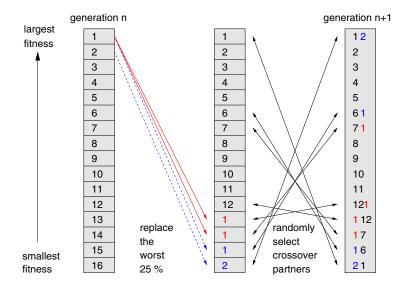

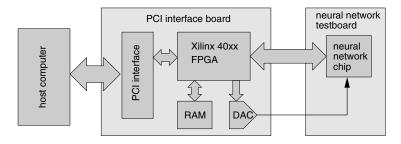

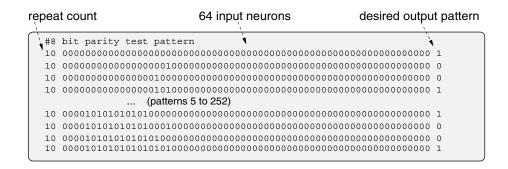

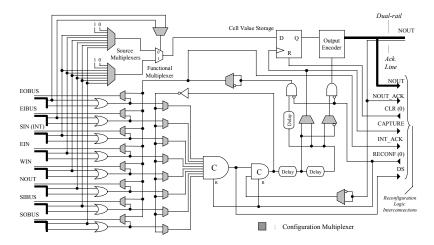

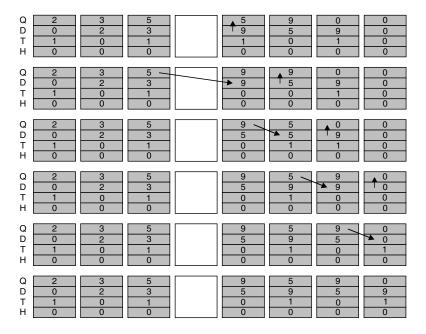

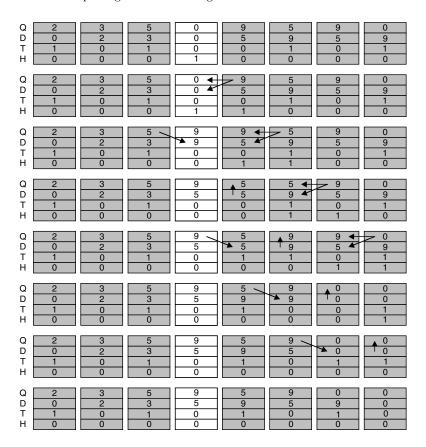

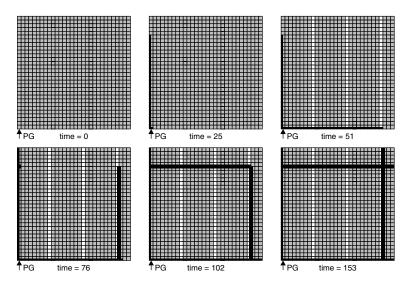

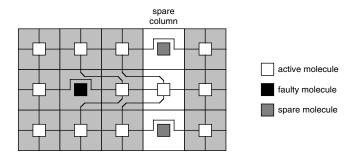

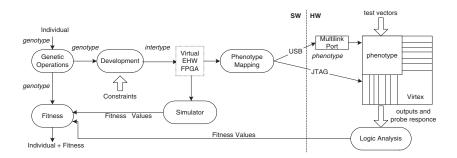

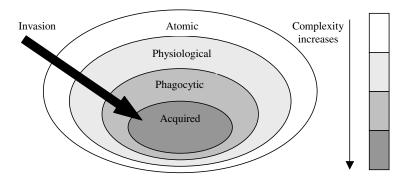

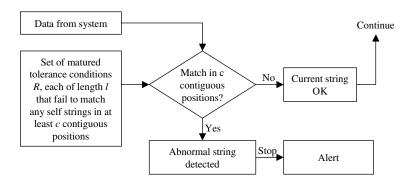

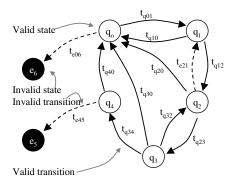

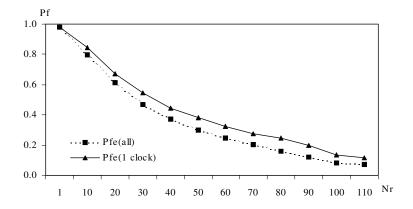

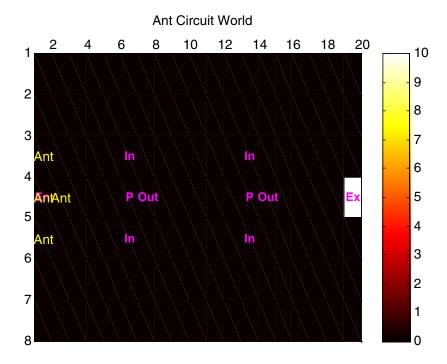

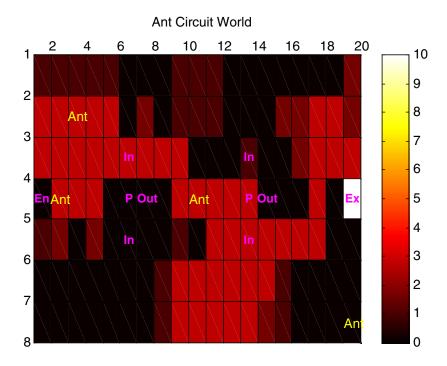

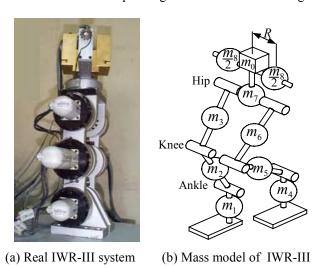

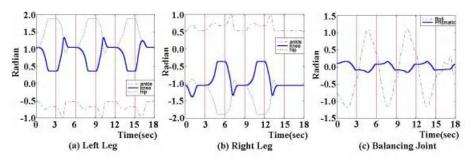

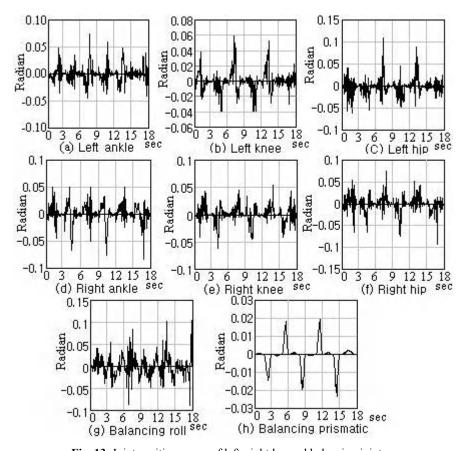

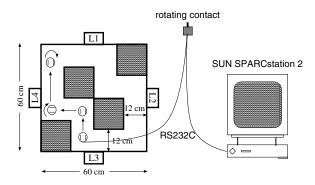

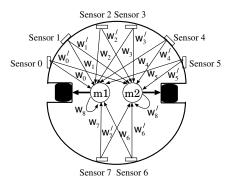

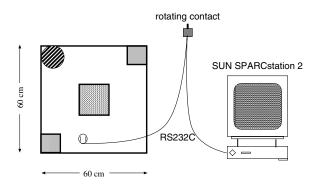

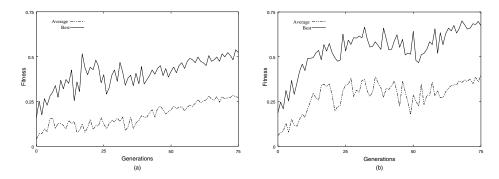

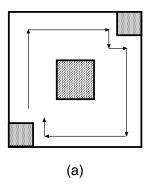

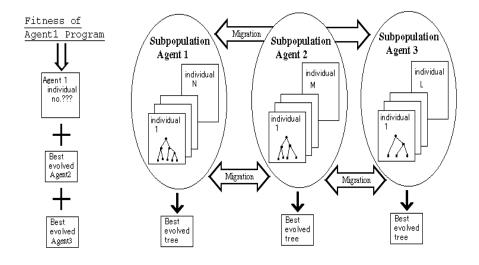

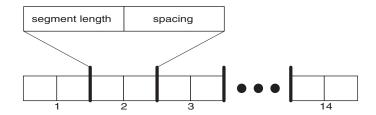

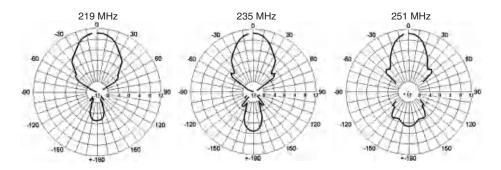

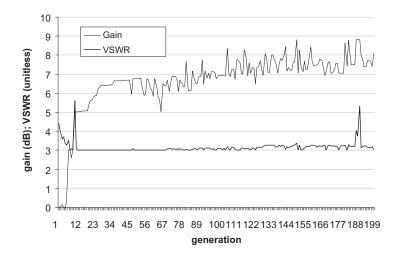

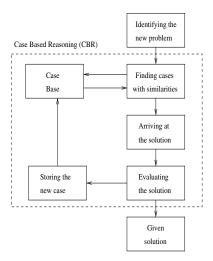

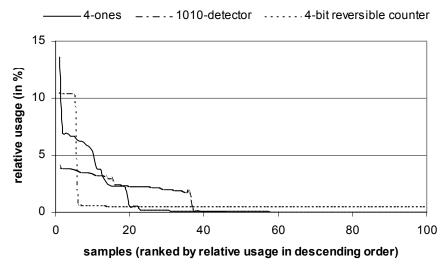

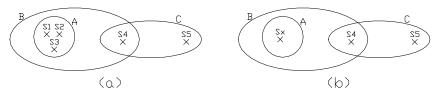

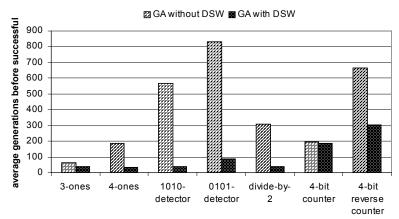

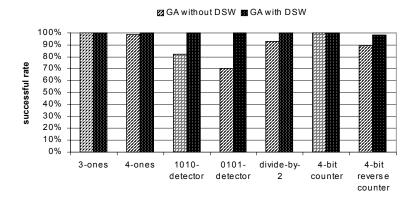

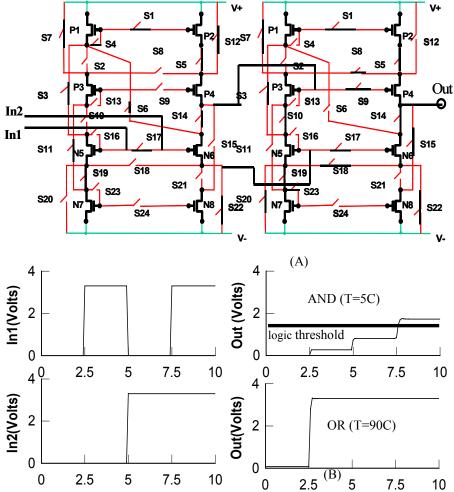

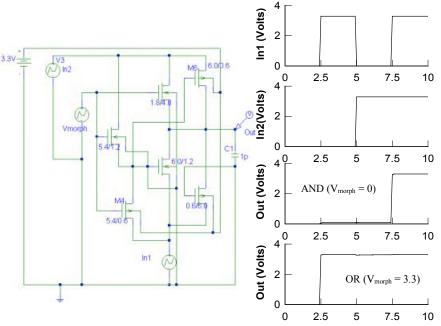

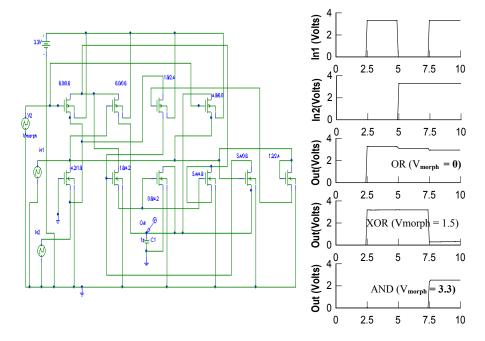

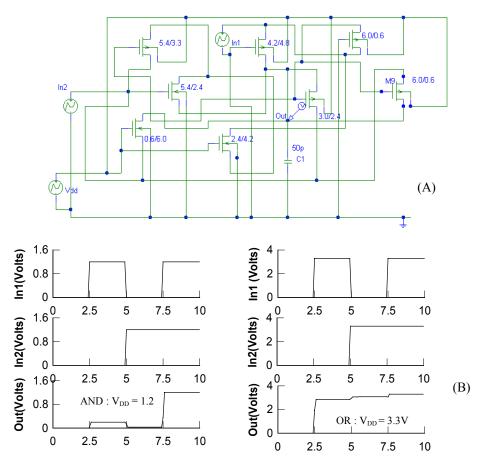

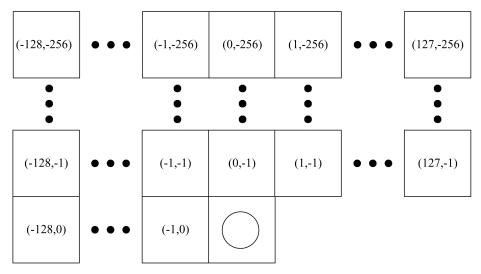

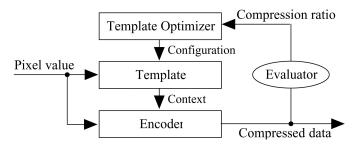

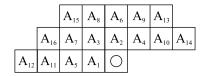

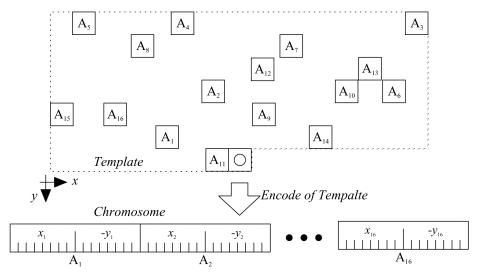

Evolutionary digital filter design has been explored in other work. Generally, the representations used are low-level, for example gate level or function block level (Miller 1999, Wilson & Mcleod 1993, Uesaka & Kawamata 2000, Uesaka & Kawamata 1999). This has the advantage that a complete filter is evolved, and additional fitness criteria (e.g. sensitivity to parameter quantisation) can be used. On the other hand, the complexity of the evolved filters is limited, typically to second or third order filters. The work presented here is aimed at constructing filters of 'real world' complexity; the examples shown are order 12 and order 15 filters.